Buy it Now https://gra-afch.com/catalog/rf-units/dds-ad9959-arduino-shield-rf-signal-generator-600-mhz-1-5-ghz-core-clock-low-spurs-low-harmonic/#prettyPhoto

Story

We have already made a similar device earlier: a single-channel dds generator based on the AD9910. But in order to do IQ modulation, several such devices (AD9910) would be needed, and a complex circuit using a synchronization distributor, for example AD9510, development of an additional board and implementation of a control program to control the synchronization mode. Because IQ modulation (and other complex modulation types) requires accurate phase synchronization. Therefore, for this project we chose a 4 channel AD9959 with synchronized outputs. Analog Devices also offers a 2 channel version, the AD9958. But for our project, we chose the AD9959 as it provides more functionality, and the difference in price is quite indicative.

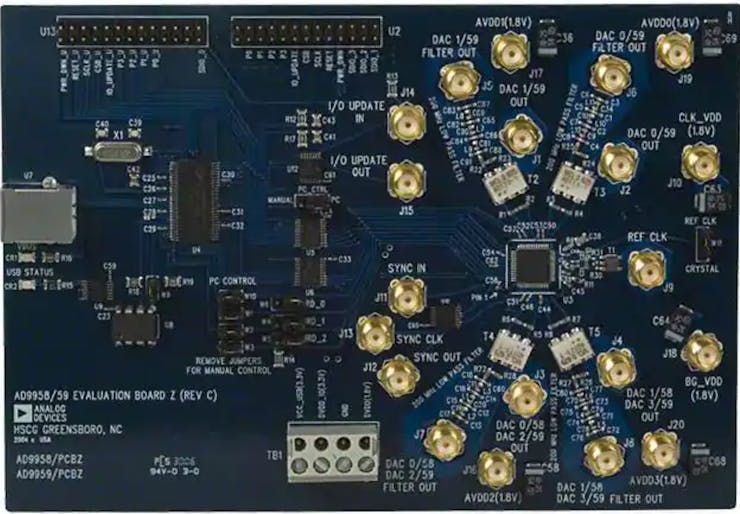

We started looking for ready-made solutions for the demo board AD9959 and immediately stumbled upon the evalution board AD9959/PCBZ from Analog Devices for $450, but this board would also require an additional power supply and an external clock source.

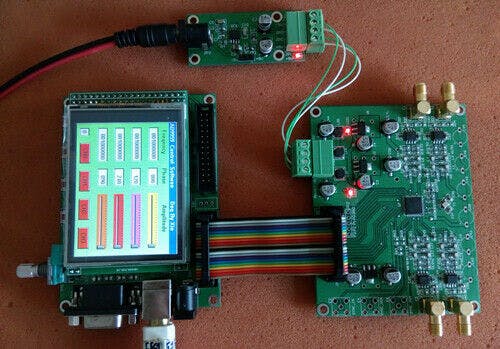

Since the option of using the original board turned out to be very expensive and complicated, and besides, there was no screen and control buttons, which means it was impossible to use such a generator independently from a computer, we decided to order a Chinese analogue for $130:

The Chinese saved some money and therefore this board did not have RF output transformers (to suppress even harmonics), and besides, it was impossible to use external reference clocking with the Chinese board. There were also unsigned buttons on the board. In the Chinese software, serious flaws were also found: The output power is set in raw 10-bit values, that is, it is impossible to understand what value of the output power is, the phase is set only in integer values, and the firmware source code is closed, so it is impossible to make changes to it yourself. And besides all of the above, this device did not work right out of the box, the seller did not help us in any way, because he simply did not respond to our messages, so we began to repair ourselves. The device only started working after we hadn't re-soldered some suspicious connections.

As a result, we were unable to use this device due to:

- 1. Large amount of spurs (due to the lack of a transformer).

- 2. Because of the inability to set the desired output level in dBm.

- 3. Due to the impossibility to set the fractional phase value.

- 4. Due to the impossibility of external clocking.

- 5. Inconvenient menu navigation.

- 6. Closed source code.

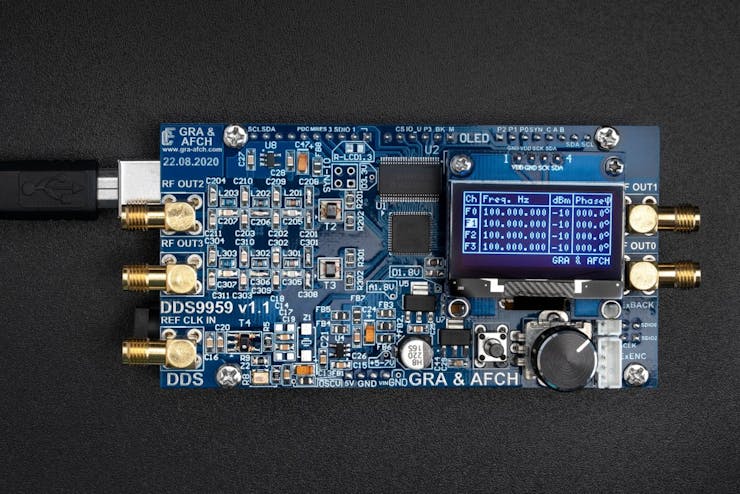

That is why we decided to create our own deviceDDS9959, devoid of all the listed disadvantages and having the following characteristics:

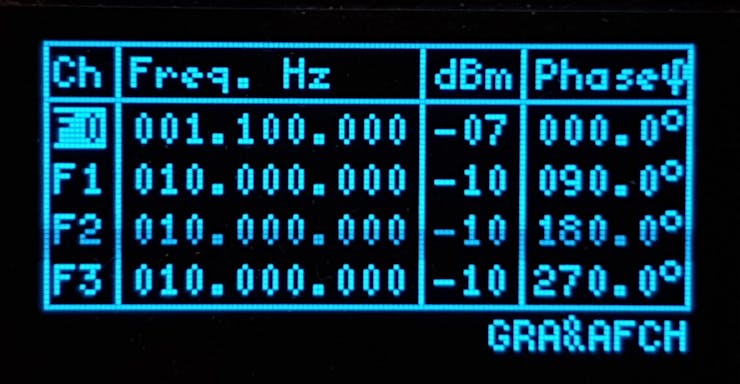

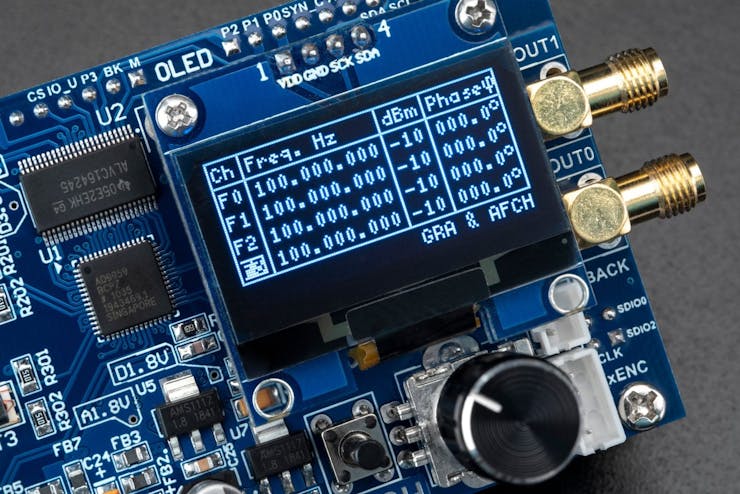

- Convenient and fast control with an encoder (easily change the frequency, power and phase of all 4 channels).

- Additional menu for setting the clock source with the possibility of overclocking. Overclocking makes it possible to get Fout = 225MHz @ up to 600 MSPS.

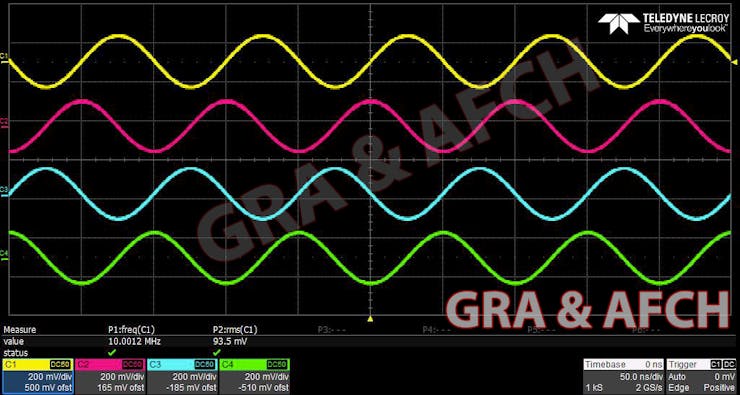

- 4 synchronized DDS channels.

- Low harmonics no more than -60 dBc. An output RF transformer is used for the correct operation of the current mirror.

- Small spurs.

- 4 layer board. Signal lines TOP and Bottom, inner layers Ground and Power.

- Low Noise LDO Stabilizers.

- Separate power supply for all analog and digital lines (1.8V and 3.3V), 5 pcs IC voltage stabilizers are used. Additionally, there is an RF Ferrite bead interchange.

- High-speed decoupling Level converter and TTL 5V matching.

- At the output of each channel is a transformer to reduce even harmonics.

- Additionally balancing transformer is used for XO, TCXO and REF CLK IN options.

- Easy to connect OLED display.

- Device control with one encoder and one button.

- The synthesizer is capable to generate sine wave.

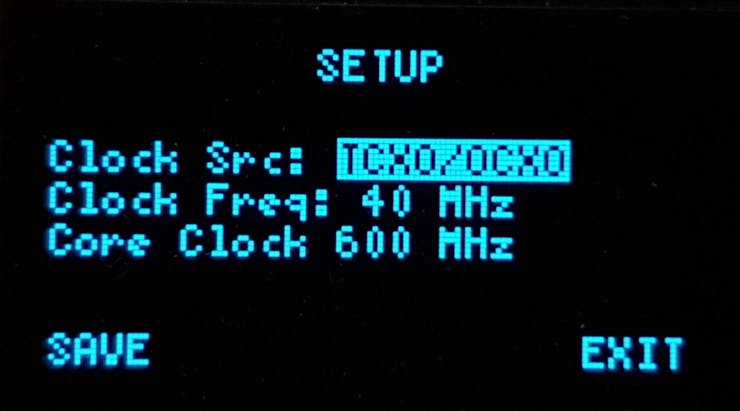

- The software allows you to select and configure the frequency of the clock generator through the user menu (without the need to recompile the program).

- Any settings can be stored in non-volatile EEPROM memory (located at Arduino Mega).

- Basic settings are applied and saved automatically.

- This shield support overclocking the AD9959 core up to 600 MHz.

- DDS AD9959 Shield has ability to generate a signal up to 225 MHz with a core overclocking up to 600 MHz (to suppress harmonics, it is recommended to overclock the AD9959 for frequencies above 200 MHz).

- XO – Crystal 25 MHz 20 ppm internal oscillator with PLL up to 600 MHz.

- TCXO – 40MHz (Supports 10 – 50 MHz) 1 ppm external oscillator PLL up to 600 MHz.

- REF CLK IN – external reference clock input, up to 600 MHz. (this source is NOT INCLUDED).

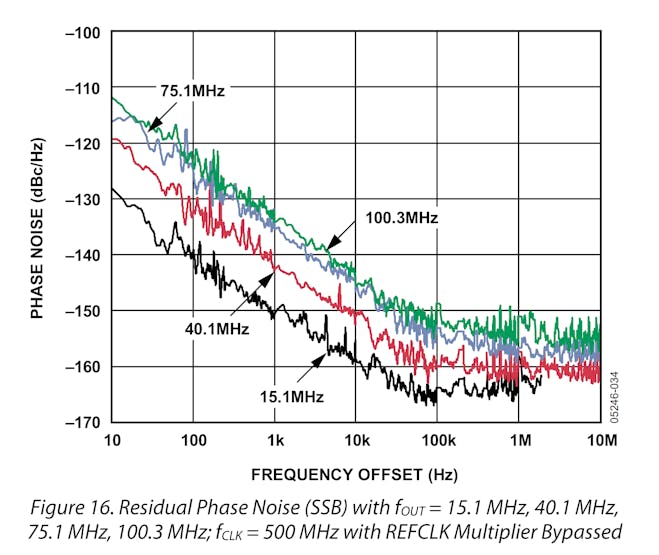

This parameter is very important and interesting for those who buy DDS.Since the intrinsic phase noise of DDS is obviously less than that of PLL generators, the final value is highly dependent on the clock source. In order to achieve the values stated in the datasheet on AD9959, when designing our DDS AD9959 Arduino Shield, we strictly adhered to all recommendations from Analog Devices: PCB layout in 4 layers, separate power supply of all 4 power lines (3.3 V digital, 3.3 V analog, 1.8 V digital, and 1.8 V analog). Therefore, when buying our DDS AD9959 Arduino Shield, You can focus on the data from the datasheet on the AD9959.

Figure 18 shows the noise level when using the built-in PLL in DDS. The PLL multiplies the frequency of a 25 MHz generator by 20 times. We use a frequency – 40 MHz (x12 Multiplier) or 50 MHz (x10 Multiplier) from TCXO which gives even more stability.

And figure 16 shows the noise level when using an external reference clock 500 MHZ, with the PLL off.

Comparing these two plots, for example, for Fout = 40.1 MHz and the internal PLL turned on at 10 kHz carrier offset, the phase noise level is -127 dBc @ 10 kHz. And with the PLL off and using external clocking, the phase noise is 155 dBc @ 10kHz. That is, when using an external clock phase noise by 28 dBc better (lower).

For the same frequency Fout = 40.1 MHz, and the internal PLL turned on at 1 MHz carrier offset, the phase noise level is -130 dBc @ 1 MHz. And with the PLL off and using external clocking, the phase noise is 160 dBc @ 1 MHz. That is, when using an external clock phase noise by 30 dBc better (lower).

Conclusion: when using external clocking, You can get much lower phase noise than using the built-in PLL. But do not forget that in order to achieve such results, increased requirements are put forward to the external generator.

OLED Display Menus:

Комментариев нет:

Отправить комментарий