ASIC Avalon2 A3255-Q48 для майнинга BitCoin mining Печатная плата PCB 16 chips 26GHs

Продам PCB печатные

платы ASIC Avalon2 A3255-Q48 на 16 чипов 26Gh/s - ПЛАТЫ ЕСТЬ В НАЛИЧИИ

( в наличии есть комплектующие PTH12040WAH и т.д.)

Цена платы от 1 шт. - $19

от 10 шт. - $17

от 100 шт. - цена договорная

Есть собранные майнеры производительность 26Gh/s ( в наличии 16 шт.)

от 1 шт. - $70

от 10 шт - цена договорная

Посмотреть как работают майнеры

http://www.youtube.com/watch?v=-QTctTFDGWQ

Оплата через практически любые системы оплаты PayPal, BitCoin, WebMoney, Яндеск Деньги, VISA, MasterCard, Итеркасса купить можно по этой ссылке

http://asic.com.ua/

http://asic-miner-buy.com/

Доставка по всему миру, время доставки 1-4 недели, цена доставка $6. Возможна доставка экспресс доставкой за 3 дня DHL, FedEX, TNT и т.д. ( все можно заказать через сайт)

Selling PCB printed circuit board ASIC Avalon2 A3255-Q48 16 chips 26Gh/s - BOARD IS AVAILABLE

(Available there PTH12040WAH components, etc.)

Price from 1 pc board. - $ 19

from 10 pcs. - $ 17

from 100 pcs. - Price negotiable

There miners collected performance 26Gh / s (available 16 pcs.)

1 pc. - $ 70

10 pcs - price negotiable

See how the miners

http://www.youtube.com/watch?v=-QTctTFDGWQ

pay through almost any payment system PayPal, BitCoin, WebMoney, VISA, MasterCard buy at this link

http://asic-miner-buy.com/

Worldwide shipping, delivery time of 1-4 weeks, the price of shipping is $ 6. Possible delivery express delivery in 3 days DHL, FedEX, TNT, etc.

Any questions, please contact us.

( в наличии есть комплектующие PTH12040WAH и т.д.)

Цена платы от 1 шт. - $19

от 10 шт. - $17

от 100 шт. - цена договорная

Есть собранные майнеры производительность 26Gh/s ( в наличии 16 шт.)

от 1 шт. - $70

от 10 шт - цена договорная

Посмотреть как работают майнеры

http://www.youtube.com/watch?v=-QTctTFDGWQ

Оплата через практически любые системы оплаты PayPal, BitCoin, WebMoney, Яндеск Деньги, VISA, MasterCard, Итеркасса купить можно по этой ссылке

http://asic.com.ua/

http://asic-miner-buy.com/

Доставка по всему миру, время доставки 1-4 недели, цена доставка $6. Возможна доставка экспресс доставкой за 3 дня DHL, FedEX, TNT и т.д. ( все можно заказать через сайт)

Selling PCB printed circuit board ASIC Avalon2 A3255-Q48 16 chips 26Gh/s - BOARD IS AVAILABLE

(Available there PTH12040WAH components, etc.)

Price from 1 pc board. - $ 19

from 10 pcs. - $ 17

from 100 pcs. - Price negotiable

There miners collected performance 26Gh / s (available 16 pcs.)

1 pc. - $ 70

10 pcs - price negotiable

See how the miners

http://www.youtube.com/watch?v=-QTctTFDGWQ

pay through almost any payment system PayPal, BitCoin, WebMoney, VISA, MasterCard buy at this link

http://asic-miner-buy.com/

Worldwide shipping, delivery time of 1-4 weeks, the price of shipping is $ 6. Possible delivery express delivery in 3 days DHL, FedEX, TNT, etc.

Any questions, please contact us.

СМОТРИМ ВИДЕО!

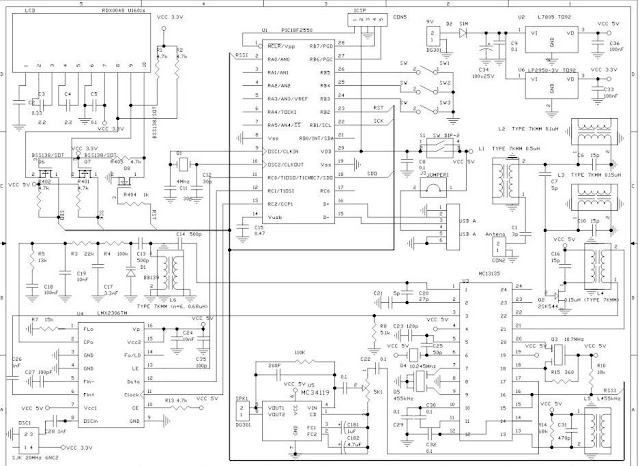

Фото 1. верхней части платы PCB A3255-Q48 16pcs

Фото 2. Нижней части платы PCB A3255-Q48 16pcs

Совсем недавно появились новые чипы ASIC A3255-Q48 от Avalon второго поколения с впечатляющей производительностью от 1.2 до 1,6 GH/s в зависимости от режима работы и напряжения питания 0,9-1.1V что дает свободу для выбора оптимального режима производительность в пересчете на Ватт.

Для получения большей производительности - ASIC A3255-Q48 предназначены для объединения в массивы по 16, 32, 64, 80, 160, 200 и более штук.

Для примера если использовать 10 плат (это 160 чипов ASIC A3255-Q48) можно получить максимальную производительность 160 х 1,6 = 256 GH/s. И это не просто расчеты - эти цифры реально подвержены тестами! ПОСМОТРИТЕ ОБЯЗАТЕЛЬНО ВИДЕО!